專用集成電路設(shè)計(jì) 定制化芯片的挑戰(zhàn)與未來

專用集成電路(Application-Specific Integrated Circuit,簡稱ASIC)設(shè)計(jì)是集成電路設(shè)計(jì)領(lǐng)域的一個(gè)重要分支,它專注于為特定應(yīng)用或功能量身定制芯片。與通用集成電路(如CPU、GPU)不同,ASIC的設(shè)計(jì)目標(biāo)是在特定任務(wù)中實(shí)現(xiàn)最優(yōu)的性能、功耗和成本平衡。

1. ASIC設(shè)計(jì)的基本流程

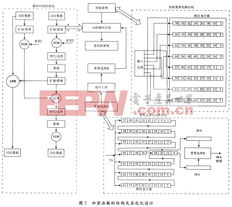

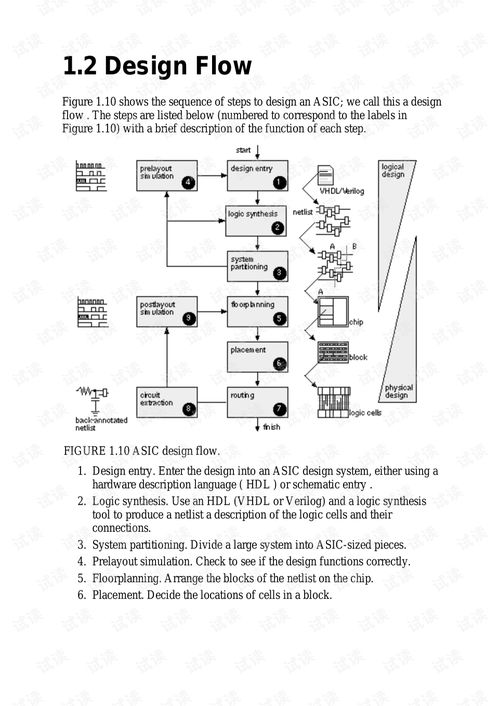

ASIC設(shè)計(jì)通常遵循一套嚴(yán)謹(jǐn)?shù)牧鞒蹋ㄐ枨蠓治觥⒓軜?gòu)設(shè)計(jì)、RTL編碼、驗(yàn)證、綜合、物理設(shè)計(jì)、制造和測試。每個(gè)環(huán)節(jié)都至關(guān)重要,直接影響芯片的最終質(zhì)量和可靠性。

- 需求分析:明確芯片的功能、性能指標(biāo)和功耗預(yù)算。

- 架構(gòu)設(shè)計(jì):確定芯片的整體結(jié)構(gòu),包括模塊劃分和接口定義。

- RTL編碼:使用硬件描述語言(如Verilog或VHDL)實(shí)現(xiàn)邏輯功能。

- 驗(yàn)證:通過仿真和形式驗(yàn)證確保設(shè)計(jì)符合規(guī)格。

- 綜合:將RTL代碼轉(zhuǎn)換為門級網(wǎng)表,優(yōu)化時(shí)序和面積。

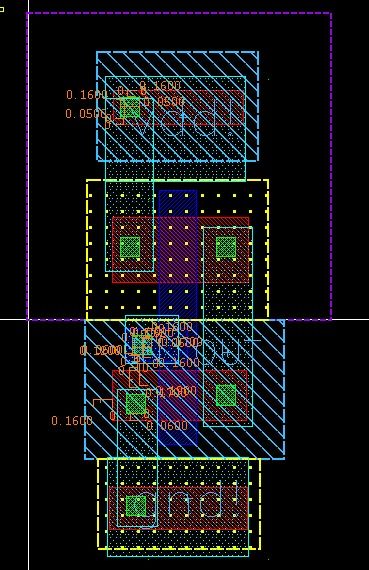

- 物理設(shè)計(jì):完成布局布線,生成可用于制造的版圖。

- 制造與測試:在晶圓廠流片,并進(jìn)行硅后測試以排除缺陷。

2. ASIC設(shè)計(jì)的優(yōu)勢與挑戰(zhàn)

ASIC的優(yōu)勢在于其高度定制化,能夠?yàn)樘囟☉?yīng)用(如人工智能、通信設(shè)備、汽車電子)提供極致性能。例如,在深度學(xué)習(xí)領(lǐng)域,專用AI芯片(如谷歌的TPU)通過優(yōu)化矩陣運(yùn)算,顯著提升了計(jì)算效率。

ASIC設(shè)計(jì)也面臨諸多挑戰(zhàn):

- 高昂的開發(fā)成本:從設(shè)計(jì)到流片可能需要數(shù)百萬至數(shù)千萬美元,適合大規(guī)模量產(chǎn)場景。

- 長開發(fā)周期:完整流程通常需要1-3年,技術(shù)迭代風(fēng)險(xiǎn)較高。

- 設(shè)計(jì)復(fù)雜性:隨著工藝節(jié)點(diǎn)向納米級演進(jìn),物理效應(yīng)(如功耗、噪聲)管理變得更加困難。

3. 技術(shù)趨勢與未來展望

ASIC設(shè)計(jì)正受益于多項(xiàng)技術(shù)進(jìn)步:

- 先進(jìn)工藝節(jié)點(diǎn):7nm、5nm甚至更小工藝使得芯片集成度更高,性能更強(qiáng)。

- 設(shè)計(jì)自動化工具:AI輔助設(shè)計(jì)工具正在縮短開發(fā)時(shí)間并優(yōu)化結(jié)果。

- 異構(gòu)集成:通過Chiplet(小芯片)技術(shù),將不同功能的模塊封裝在一起,提升靈活性和成本效益。

隨著物聯(lián)網(wǎng)、5G和自動駕駛等領(lǐng)域的爆發(fā),ASIC需求將持續(xù)增長。開源EDA工具和RISC-V等開放指令集架構(gòu)的興起,可能降低設(shè)計(jì)門檻,推動更多創(chuàng)新。

###

專用集成電路設(shè)計(jì)是推動現(xiàn)代科技發(fā)展的核心引擎之一。盡管面臨成本和技術(shù)挑戰(zhàn),但其在性能與能效方面的不可替代性,確保了它將在智能化時(shí)代繼續(xù)扮演關(guān)鍵角色。對于設(shè)計(jì)者而言,平衡創(chuàng)新與風(fēng)險(xiǎn),擁抱技術(shù)變革,將是制勝未來的關(guān)鍵。

如若轉(zhuǎn)載,請注明出處:http://www.gzclyk.cn/product/70.html

更新時(shí)間:2026-02-23 04:47:31