集成電路中低功耗乘法器的實現與設計

隨著移動通信、物聯網、可穿戴設備等領域的飛速發展,對集成電路的性能和功耗提出了更為苛刻的要求。乘法器作為數字信號處理、圖像處理、人工智能加速器等核心運算單元中的關鍵部件,其功耗往往占據整個系統功耗的相當大比重。因此,研究與設計高性能、低功耗的乘法器,對于實現高效能的片上系統(SoC)和延長便攜式設備的電池續航時間具有至關重要的意義。

一、低功耗設計挑戰與設計層次

在深亞微米乃至納米工藝節點下,集成電路的功耗主要由動態功耗、靜態功耗和短路功耗三部分組成。對于乘法器這類頻繁進行數據運算的模塊,動態功耗是其功耗的主要來源。低功耗設計是一個系統工程,需要從系統架構、算法、電路結構乃至物理版圖等多個層面進行協同優化。

- 系統與算法級:在最高抽象層次,可以通過選擇合適的算法來減少乘法操作的次數或復雜度。例如,采用分布式算法、Booth編碼算法等,可以從根本上減少部分積的生成數量,從而降低后續加法樹壓縮的規模和功耗。

- 架構與RTL級:此層級的設計包括選擇適合的乘法器結構(如陣列乘法器、樹形乘法器)、采用門控時鐘技術、操作數隔離、動態電壓頻率調節(DVFS)等。門控時鐘可以精準地關閉乘法器在空閑周期內的時鐘網絡,消除不必要的時鐘翻轉功耗。

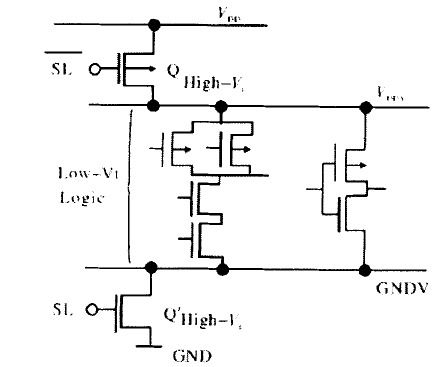

- 電路與邏輯級:采用低功耗邏輯單元,如傳輸門邏輯、多米諾邏輯的優化變種,或者使用多閾值電壓(Multi-Vt)庫,在關鍵路徑使用低閾值電壓單元保證速度,在非關鍵路徑使用高閾值電壓單元降低漏電。優化晶體管尺寸(尺寸縮放)也是常用手段。

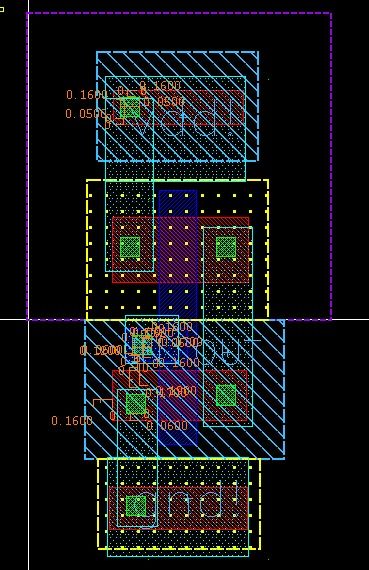

- 物理版圖級:通過精細的布局布線,減少關鍵長互連線的電容,從而降低其翻轉功耗。采用電源門控技術,在乘法器長時間不工作時,可以切斷其電源供應,近乎消除靜態功耗。

二、關鍵實現技術與結構

- Booth編碼算法:這是一種廣泛用于減少部分積數量的算法。通過將乘數重編碼為有符號數字,可以將連續“1”的序列轉換為更少的運算操作(如“+M, 0, -M”),典型情況下能將部分積數量減少近一半,顯著降低了部分積累加陣列的規模和功耗。改進的基-4 Booth編碼是其高效實現之一。

- Wallace樹與壓縮樹結構:部分積生成后,需要將其壓縮求和。Wallace樹采用全加器(3:2壓縮器)和半加器以樹形結構快速壓縮部分積,其結構不規則但速度快。為了平衡速度與規整性,4-2壓縮器被廣泛用于構建規整的壓縮樹(如Dadda樹),它在保持高速的更利于自動布局布線,并能減少中間節點的開關活動性。

- 近似計算技術:在允許一定計算誤差的應用場景(如圖像處理、機器學習推理),近似乘法器可以大幅降低功耗。通過截斷不重要的部分積、簡化壓縮樹結構或使用近似的加法器單元,可以在可接受的精度損失下,實現功耗和面積的顯著優化。

- 異步電路設計:與全局同步時鐘驅動的電路不同,異步乘法器采用握手協議進行局部通信和數據傳遞。它消除了全局時鐘樹帶來的巨大功耗,并且僅在有數據活動時消耗能量,無空轉功耗。雖然設計復雜,但在極致低功耗場景下潛力巨大。

三、設計流程與權衡

設計一個低功耗乘法器并非單純追求功耗最低,而需要在功耗(Power)、性能(Performance)、面積(Area)和精度(Accuracy) 之間取得最佳平衡,即所謂的PPAA權衡。

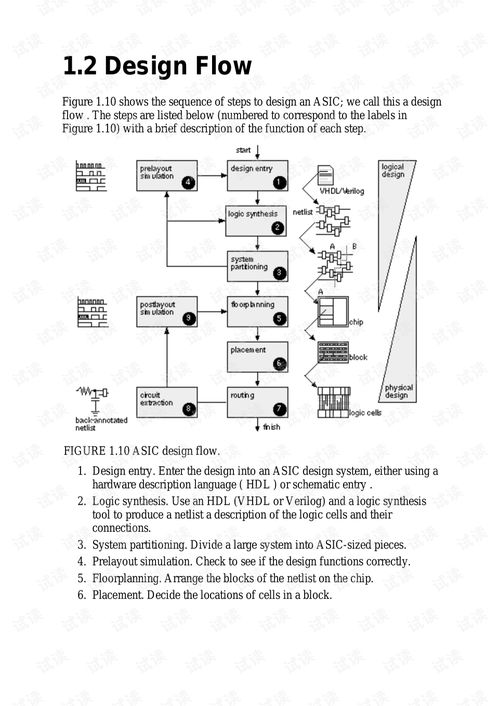

設計流程通常從系統需求分析開始,確定所需的精度(如整型、浮點型、位寬)和性能指標(如最大工作頻率、吞吐率)。然后,在算法和架構層面進行探索,選擇合適的基礎算法和整體結構。接著,使用硬件描述語言(如Verilog/VHDL)進行RTL實現,并集成門控時鐘等低功耗設計意圖。之后,通過邏輯綜合工具,結合多閾值電壓庫和時鐘門控插入策略,生成門級網表。在物理實現階段,利用布局布線工具進行精細優化,并可能引入電源門控。需要通過仿真和功耗分析工具(如PrimeTime PX)在不同向量下進行嚴格的功耗驗證。

四、未來展望

面向低功耗乘法器的設計將面臨工藝持續微縮帶來的量子效應、漏電問題加劇以及新興計算范式的挑戰。一方面,新器件(如FinFET, GAA FET)和新材料為電路設計帶來了新的機遇;另一方面,存內計算、模擬計算等非馮·諾依曼架構試圖從根本上打破“內存墻”和功耗限制,將乘法運算與存儲結合,這為超低功耗乘加運算開辟了全新的技術路徑。面向特定領域(如AI)的定制化近似乘法器也將持續成為研究熱點。

集成電路中低功耗乘法器的設計與實現是一個多層級、多技術融合的復雜課題。工程師必須深入理解從算法到物理的整個設計鏈,靈活運用各種低功耗技術,才能在滿足嚴苛性能要求的打造出能效比卓越的運算核心單元,推動電子系統向著更智能、更綠色的方向發展。

如若轉載,請注明出處:http://www.gzclyk.cn/product/60.html

更新時間:2026-02-23 19:22:15