數(shù)字電路基礎(chǔ) IC設(shè)計中的存儲器件——從鎖存器、觸發(fā)器到寄存器

在集成電路(IC)設(shè)計中,存儲器件是實現(xiàn)數(shù)據(jù)存儲、狀態(tài)保持與同步操作的核心組件,是構(gòu)成復(fù)雜數(shù)字系統(tǒng)(如處理器、存儲器陣列和通信模塊)的基礎(chǔ)。它們主要分為鎖存器、觸發(fā)器和寄存器三大類,雖然功能相似,但在工作原理、時序特性和應(yīng)用場景上存在顯著差異。理解這些器件是掌握數(shù)字系統(tǒng)設(shè)計的關(guān)鍵。

一、鎖存器:電平敏感的存儲單元

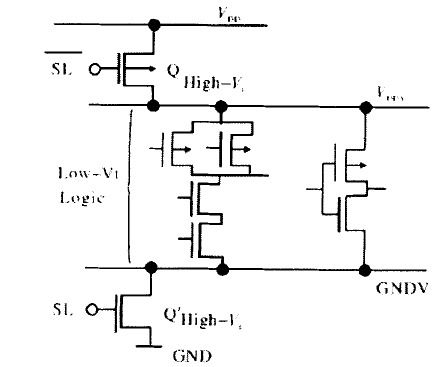

鎖存器是基本的存儲元件,其狀態(tài)由控制信號的電平直接控制。最常見的類型是D鎖存器。當使能信號(如時鐘CLK或使能EN)為有效電平(通常為高電平)時,輸出Q會實時跟隨輸入D的變化,相當于一個透明的“門”;當使能信號變?yōu)闊o效電平(如低電平)時,輸出Q將鎖定在使能信號跳變前一刻的輸入值,并保持不變,從而實現(xiàn)數(shù)據(jù)存儲。

鎖存器的優(yōu)點是結(jié)構(gòu)簡單,但存在“透明”特性,即在使能期間輸入變化會直接傳播到輸出,易在時序電路中引發(fā)競爭冒險和亞穩(wěn)態(tài)問題。因此,在現(xiàn)代同步IC設(shè)計中,鎖存器通常用于特定場景,如數(shù)據(jù)鎖存、總線保持,或作為更復(fù)雜觸發(fā)器的一部分。

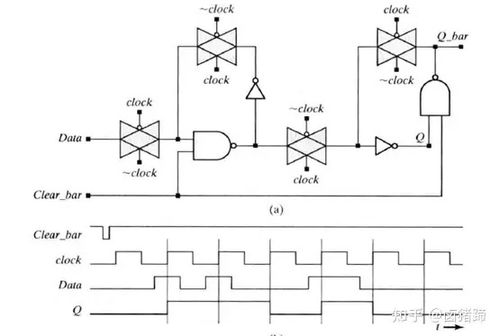

二、觸發(fā)器:邊沿觸發(fā)的存儲單元

觸發(fā)器是同步數(shù)字電路中最常用的存儲器件,其核心特點是狀態(tài)變化僅發(fā)生在時鐘信號的邊沿(上升沿或下降沿),從而有效避免鎖存器的透明性問題。最典型的代表是D觸發(fā)器。

在時鐘有效邊沿到來時,觸發(fā)器會采樣該時刻的輸入D值,并將其輸出到Q,而在時鐘的其他時刻,無論D如何變化,輸出Q均保持不變。這種邊沿觸發(fā)機制確保了數(shù)據(jù)的穩(wěn)定捕獲和同步,大大增強了電路的可靠性和時序可控性。

觸發(fā)器通常還包含異步控制端,如置位(SET,強制輸出為1)和復(fù)位(RESET,強制輸出為0),這些控制信號獨立于時鐘,用于初始化或強制狀態(tài)。在IC設(shè)計中,觸發(fā)器是構(gòu)成時序邏輯(如狀態(tài)機、計數(shù)器、流水線寄存器)的基本單元。

三、寄存器:多位觸發(fā)器的集合

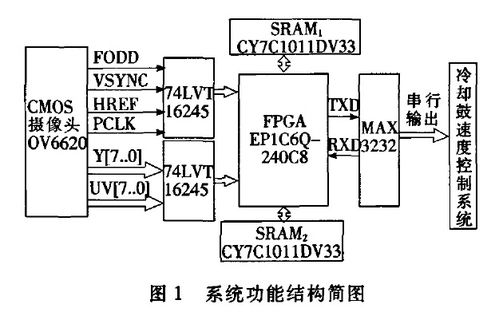

寄存器由一組(通常是多位,如8位、16位、32位)觸發(fā)器并行構(gòu)成,共享同一個時鐘和控制信號,用于同時存儲和操作一個數(shù)據(jù)字或指令。例如,一個8位寄存器包含8個D觸發(fā)器,每個存儲1位數(shù)據(jù),共同構(gòu)成一個8位存儲單元。

寄存器在微處理器和數(shù)字系統(tǒng)中無處不在,用途包括:

- 數(shù)據(jù)暫存:如通用寄存器組,用于算術(shù)邏輯單元(ALU)的臨時數(shù)據(jù)存儲。

- 狀態(tài)保持:如狀態(tài)寄存器、控制寄存器。

- 接口緩沖:如輸入/輸出(I/O)寄存器。

寄存器設(shè)計需考慮多位數(shù)據(jù)的一致性、時鐘偏移(skew)和功耗優(yōu)化。

四、在集成電路設(shè)計中的考量

在IC設(shè)計流程(從RTL設(shè)計到物理實現(xiàn))中,存儲器件選擇與優(yōu)化至關(guān)重要:

- 時序收斂:需滿足建立時間(Setup Time)和保持時間(Hold Time)的要求,確保數(shù)據(jù)在時鐘邊沿被正確采樣。

- 面積與功耗:觸發(fā)器比鎖存器結(jié)構(gòu)復(fù)雜,通常占用更多面積和功耗。設(shè)計時需在性能、面積和功耗之間權(quán)衡,例如在高速路徑使用觸發(fā)器以保證穩(wěn)定,在非關(guān)鍵路徑可能使用鎖存器以節(jié)省面積。

- 時鐘樹設(shè)計:寄存器的時鐘信號需要通過精心設(shè)計的時鐘樹網(wǎng)絡(luò)分發(fā),以最小化時鐘偏移和抖動。

- 可測性設(shè)計:通常通過掃描鏈技術(shù)將寄存器連接成鏈,以便在生產(chǎn)測試中注入和觀測數(shù)據(jù)。

- 物理布局:存儲單元通常作為標準單元庫的一部分,布局需考慮連線長度、寄生效應(yīng)和熱分布。

###

從鎖存器到觸發(fā)器,再到寄存器,這些存儲器件構(gòu)成了數(shù)字IC存儲層次的基石。鎖存器的電平敏感特性適用于特定控制邏輯,觸發(fā)器的邊沿觸發(fā)機制奠定了同步設(shè)計的主流范式,而寄存器則是數(shù)據(jù)通路與控制通路的實際載體。優(yōu)秀的IC設(shè)計師必須深入理解它們的原理、特性與應(yīng)用場景,方能在芯片設(shè)計中實現(xiàn)性能、面積與功耗的完美平衡,打造出高效可靠的集成電路系統(tǒng)。

如若轉(zhuǎn)載,請注明出處:http://www.gzclyk.cn/product/51.html

更新時間:2026-02-23 05:01:41